The AP0100CS integrates ApTIna's advanced image processing pipeline with stunning video and low light performance. With the advanced Local Tone Mapping (ALTM) function for wide dynamic range image rendering, high quality video can be generated even under very difficult high contrast lighting conditions. The AP0100CS integrates an NTSC/PAL encoder with advanced converter functionality to provide the high TV line resolution required to simulate the CCTV market.

This product provides designers in the Chinese market with new camera designs that were not available in the past; that is, they can be used in analog CCTV surveillance with high resolution, inherently superior low-light performance and WDR capabilities of high-end IP camera sensors. . This powerful design flexibility will bring exciting new surveillance cameras.

Typical operationA typical READ or WRITE sequence begins by the master generaTIng a start condiTIon on the bus. After the start condiTIon, the master sends the 8-bit slave address/data direction byte. The last bit indicates whether the request is for a READ or a WRITE, where a "0" indicates a WRITE and a "1" indicates a READ. If the address matches the address of the slave device, the slave device acknowledges receipt of the address by generating an acknowledge bit on the bus.

If the request was a WRITE, the master then transfers the 16-bit register address to which a WRITE will take place. This transfer takes place as two 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte The master will then transfer the 16-bit data, as two 8-bit sequences and the slave sends an acknowledge bit after each sequence to indicate that the byte has been received. The master stops writing by generating a (re) Start or stop condition. If the request was a READ, the master sends the 8-bit write slave address/data direction byte and 16-bit register address, just as in the write request. The master then generates a (re)start condition And the 8-bit read slave address/data direction byte, and clocks out the register data, 8 bits at a time. The master transfer an acknowledge bit after each 8-bit transfer. The data transfer is stopped when the master sends a no -acknowledge bit.

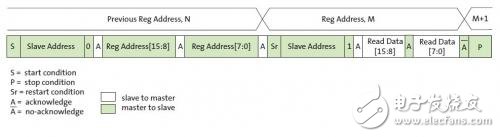

Single random readingFigure 1 shows the typical READ cycle of the host to the address. The first two bytes sent by the host are an internal 16-bit register address. The following 2-byte READ cycle sends the contents of the registers to host.

Figure 1: Single READ from Random Location

Single current position readingFigure 2 shows the single READ cycle without writing the address. The internal address will use the previous address value written to the register.

Figure 2: Single Read from Current Location

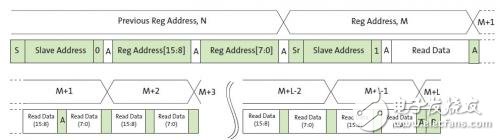

Connect from any locationThis sequence (Figure 3) starts in the same way as the single READ from random location . Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generate an acknowledge bit and continues to perform byte READs until "L" bytes have been read.

Figure 3: Sequential READ, Start from Random Location

Connect reading from the current positionThis sequence (Figure 4) starts in the same way as the single READ from current location (Figure 2). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generate an acknowledge bit and continues to Perform byte reads until "L" bytes have been read.

Figure 4: Sequential READ, Start from Current Location

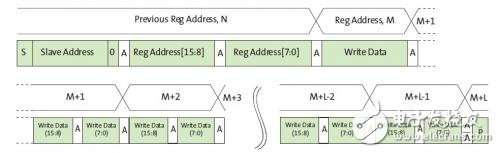

Write to any positionFigure 5 shows the typical WRITE cycle from the host to the AP0100CS. The first 2 bytes indicate a 16-bit address of the internal registers with most-significant byte first. The following 2 bytes indicate the 16-bit data.

Figure 5: Single WRITE to Random Location

Continuous writing from any positionThis sequence (Figure 6) starts in the same way as the single WRITE to random location (Figure 5). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generate an acknowledge bit and continues to Perform byte writes until "L" bytes have been written. The WRITE is terminated by the master generating a stop condition.

Figure 6: Sequential WRITE, Start at Random Location

Our Lithium Battery includes 5G Base Station Backup Power System,like 48V 100Ah/150Ah/200Ah Lithium Battery. 3.2V Prismatic cells,like 3.2V 50Ah/105Ah/202Ah Lithium Battery. And Lithium Ion Pouch Cells, including 3.2V 12-30Ah.

Lifepo4 Battery,Lifepo4 Lithium Ion Battery,Lifepo4 48V 100Ah Lithium Ion Battery,Lithium Ion Battery For Solar 100Ah

Jiangsu Zhitai New Energy Technology Co.,Ltd , https://www.zhitainewenergy.com