"Watchdog", the hardware is actually a timer, usually composed of a counter with its own pulse source, or a monostable circuit. When the CPU is working normally, it outputs a pulse every other time to trigger the one-shot circuit. As long as the transient steady-state duration is longer than the trigger period of the CPU, the monostable system cannot return to the steady state. After the CPU is in an infinite loop, it will not trigger the one-shot system, and it will return to the steady state. The signal outputted when returning to the steady state is used as the reset signal to make the CPU exit the infinite loop.

The "watchdog" has the following characteristics:(1) It can work independently and does not depend on the CPU. (2) The CPU interacts with the "watchdog" system at a fixed time interval to indicate "system is normal". (3) When the CPU falls into an infinite loop, it can be discovered in time and the system is reset.

In the enhanced 51 series MCU, there is a "watchdog" on the chip, which is very convenient to use. In a normal type of microcontroller (such as 89C2051), there is no watchdog, which must be established by the user.

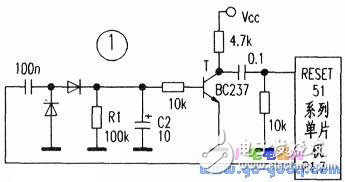

Figure 1 shows a "watchdog" circuit with a single-stable configuration. P1.7 periodically outputs a square wave signal to charge C2, T1 is turned on, and the output is low, which does not reset the microcontroller. Once the CPU falls into an infinite loop, P1.7 no longer outputs a square wave at regular intervals. C2 discharges through R1, T1 is turned off, the output goes high, and the microcontroller is reset.

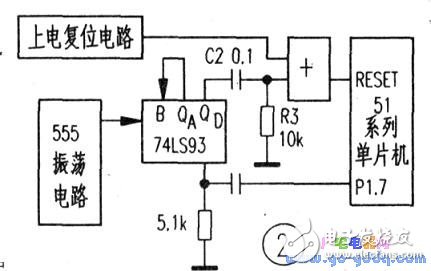

Figure 2 shows the counting type watchdog circuit. 555 is connected to a multivibrator (cycle is T0), 74LS93 is connected to a hexadecimal counter, and when the eighth pulse is counted, QD goes high. The MCU outputs a clear pulse from P1.7. As long as the interval of the pulse is shorter than 8 pulse periods, the counter always counts less than 8. The QD terminal is kept low. When the CPU falls into an infinite loop, the output pulse cannot be cleared. The counter counts to 8, and the QD terminal immediately goes high. After the differential circuits C2 and R3, a positive pulse is output to reset the CPU.

Square Hole Breadboard,400 Tie Point Breadboard,Makeronics Breadboard,Small Solderless Breadboard

Cixi Zhongyi Electronics Factory , https://www.zybreadboard.com